# **Qseven<sup>®</sup> Specification**

Qseven<sup>®</sup> pinout, electromechanical description and implementation guidelines

Version 2.0 September 20, 2012

© Copyright 2013, SGeT Standardization Group for Embedded Technology e.V.

Note that some content of this specification may be legally protected by patents rights not held by SGeT. SGeT is not obligated to identify the parts of this specification that require licensing or other legitimization. SGeT specifications prospective are advisory only. Users of the SGeT are responsible for protecting themselves against liability for infringement of patents.

All content and information within this document are subject to change without prior notice. SGeT provides no warranty with regard to this user's guide or any other information contained herein and hereby expressly disclaims any implied warranties of merchantability or fitness for any particular purpose with regard to any of the foregoing. SGeT assumes no liability for any damages incurred directly or indirectly from any technical or typographical errors or omissions contained herein or for discrepancies between the product and the user's guide. In no event shall SGeT be liable for any incidental, consequential, special, or exemplary damages, whether based on tort, contract or otherwise, arising out of or in connection with this user's guide or any other information contained herein or the use thereof.

# **Revision History**

| Revision | Date (yyyy-mm-dd) | Author                         | Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 2008-07-01        | Qseven® Consortium             | Official Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.1      | 2008-08-04        | Qseven <sup>®</sup> Consortium | Corrected overall height dimension in Figure 1-1 Overall<br>Height including Heatspreader of the Qseven <sup>®</sup> Module.<br>Changed pin assignment in Figure 1-3 Edge Connector<br>Dimensions of the Qseven <sup>®</sup> Module from Pin 1 to Pin 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.11     | 2008-11-26        | Qseven <sup>®</sup> Consortium | Corrected the part numbers for the Foxconn connectors<br>and added the part numbers for the Speedtech connectors<br>listed in Table 1-1 MXM Connector. Added mounting hole<br>dimensions for bottom side to Figure 1-2 Mechanical<br>Dimensions of the Qseven® Module. Corrected and added<br>more dimensions to Figure 1-3 Edge Connector<br>Dimensions of the Qseven® Module. Added THRMTRIP#<br>signal description to Table 3-19 Signal Definition Thermal<br>Management. Renamed pin 91 from USB_CL_PRES to<br>USB_HOST_PRES#. Added pin 92 USB_HC_SEL to<br>Table 3-1 Connector Pinout Description<br>and the definition of this signal to Table 3-7 Signal<br>Definition USB. Added pin 204 MFG_NC4 to Table 3-1<br>Connector Pinout Description. Removed signal pin 56<br>SDIO_PWRSEL because it is obsolete according to the<br>current SDIO specification and set it to RSVD. Changed<br>the signal description for SDIO_WP I/O column in table 3-<br>8 SDIO Interface Signals from O to I/O. Changed<br>reference to Winbond 83627DHG. Added the<br>information about BIOS support for the MAX5362 DAC to<br>section 5.2.7 LCD Control.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.20     | 2010-08-12        | Qseven <sup>®</sup> Consortium | Changed component height value for carrier board components located under Qseven® module. Added Figure 1-1. Added section 1.1.4 Connector and Cooling Plate Keep-Out and Figure 1-6. Added note and updated connector vendor list in Table 1-1 to include only Qseven® Consortium members. Reduced minimum PCI Express links from 2 to 1, the minimum LPC Bus from 1 to 0 and the minimum HDA/AC'97 interface from 1 to 0 in Table 2-1. Added ARM/RISC Based Minimum Configuration column to Table 2-1. Changed note in section 3.2 Input Power Requirements. Changed note in section 3.2 Input Power Requirements. Changed note in section 3.2 Input Power Requirements. Changed note in order to be compliant with OTG specification and defined alternative functionality for pins 41, 123, 125, 127, 194, 195, and 196. Also in Table 3-1 changed pin 129 from RSVD to CAN0_TX and pin 130 from RSVD CAN0_RX, pins 199-203 changed from RSVD to SPI interface pins. Added important note to Table 3-2. Changed name and the signal description in Table 3-7 for USB_HOST_PRES# to USB_CC and BIOS_DISABLE#/BOOT_ALT# and changed the name of USB_HC_SEL to USB_ID. Changed I/O type in Table 3-5 for GBE_LINK#, GBE_LINK100#, GBE_LINK1000# and GBE_ACT# from OD to PP. Changed I/O type for RSTBTN#, BATLOW#, WAKE#, SLP_BTN#, LID_BTN#, and WDTRIG# from OD to CMOS. Added AC'97 support to Table 3-9. Added CAN Bus Interface Signals section 3.1.12 and Table 3-14. Changed description for pins MFG_NC04 in Table 3-20. Updated section 5.2. |

| Revision | Date (yyyy-mm-dd) | Author                         | Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|-------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0      | 2012-09-20        | Qseven <sup>®</sup> Consortium | Updated section 1 with the reduced allowable component<br>height on the bottom side of the Qseven module. Updated<br>MXM connector manufacturer Table 1-1. Added Yamaichi<br>footprint proposal (Figure 1-11). Combined DP and HDMI<br>hot plug detection signal on pin 153. Introduced µQseven<br>with 70x40 mm outline. Updated Figure 1-1, Figure 1-2<br>and Figure 1-6. Added Figure 1-4, Figure 1-7 and Figure<br>1-11. Changed I2C_CLK to GP0_I2C_CLK. Changed<br>I2C_DAT to GP0_I2C_DAT. Added GPIOs to LPC bus<br>interface. Updated I/O status in Table 3-13 to I/O. Pin<br>132/134 and 144/146 are set to RSVD (differential pair).<br>Set pin 124 to 1-wire-bus. Set 154 to RSVD. Deleted<br>Express Card and SDVO Interface of Qseven® module<br>from Table 3-1. Deleted MXM connector dimensions figure<br>from specification. Added USB3.0, I2S, UART, eDP, One-<br>Wire-Bus in Table 3-1. Updated SATA Gen1 Signal<br>Budget in Table 4-3. Added Table 4-4 SATA Gen2 Signal<br>Budget. Updated USB2.0 Signal Budget in Table 4-5. |

| 2.0 SGeT | 2013-02-23        | SGeT e.V.                      | Added SGeT Copyright page. Updated disclaimers and header/footer layout following SGeT Guidelines. Technical Content unchanged.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# Preface

## Qseven<sup>®</sup>Concept

The Qseven<sup>®</sup> concept is an off-the-shelf, multi vendor, Single-Board-Computer that integrates all the core components of a common PC and is mounted onto an application specific carrier board. Qseven<sup>®</sup> modules have a standardized form factor of 70mm x 70mm and have specified pinouts based on the high speed MXM system connector that has a standardized pinout regardless of the vendor. The Qseven<sup>®</sup> module provides the functional requirements for an embedded application. These functions include, but are not limited to, graphics, sound, mass storage, network and multiple USB ports. A single ruggedized MXM connector provides the carrier board interface to carry all the I/O signals to and from the Qseven<sup>®</sup> module. This MXM connector is a well known and proven high speed signal interface connector that is commonly used for high speed PCI Express graphics cards in notebooks.

Carrier board designers can utilize as little or as many of the I/O interfaces as deemed necessary. The carrier board can therefore provide all the interface connectors required to attach the system to the application specific peripherals. This versatility allows the designer to create a dense and optimized package, which results in a more reliable product while simplifying system integration. Most importantly, Qseven<sup>®</sup> applications are scalable, which means once a product has been created there is the ability to diversify the product range through the use of different performance class Qseven<sup>®</sup> modules. Simply unplug one module and replace it with another, no redesign is necessary.

Qseven<sup>®</sup> offers the newest I/O technologies on this minimum size form factor. This includes serial high speed buses such as:

- PCI Express<sup>™</sup>

- USB 3.0

- Serial ATA ®

- Secure Digital I/O interface

- DisplayPort<sup>™</sup>, TMDS

- USB 2.0

- High Definition Digital Audio (HDA) Integrated Interchip Sound (I2S)

- LPC interface

- Gigabit Ethernet

- LVDS Display Interface

Plus additional control and power management signals.

### Disclaimer

The information contained within this Qseven<sup>®</sup>Specification, including but not limited to any product specification, is subject to change without notice.

SGeT e.V. provides no warranty with regard to this Qseven<sup>®</sup> Specification or any other information contained herein and hereby expressly disclaims any implied warranties of merchantability or fitness for any particular purpose with regard to any of the foregoing. SGeT e.V. assumes no liability for any damages incurred directly or indirectly from any technical or typographical errors or omissions contained herein or for discrepancies between the product and the Qseven<sup>®</sup>interface specification. In no event shall SGeT e.V. be liable for any incidental, consequential, special, or exemplary damages, whether based on tort, contract or otherwise, arising out of or in connection with this Qseven<sup>®</sup>interface specification or any other information contained herein or the use thereof.

#### Intended Audience

This Qseven<sup>®</sup>electromechanical specification is intended for technically qualified personnel. It is not intended for general audiences.

### Symbols

The following symbols may be used in this specification:

## Warning

Warnings indicate conditions that, if not observed, can cause personal injury.

# Caution

Cautions warn the user about how to prevent damage to hardware or loss of data.

Note Note

Notes call attention to important information that should be observed.

### Copyright Notice

Copyright © 2008, 2012, 2013 SGeT e.V.. All rights reserved. All text, pictures and graphics are protected by copyrights. No copying is permitted without written permission from SGeT e.V. .

SGeT e.V. has made every attempt to ensure that the information in this document is accurate yet the information contained within is supplied "as-is".

### Trademarks

Product names, logos, brands, and other trademarks featured or referred to within this specification, the SGeT or the Qseven<sup>®</sup> website, are the property of their respective trademark holders. These trademark holders are not affiliated with the SGeT e.V., Qseven<sup>®</sup> products, the SGeT or the Qseven<sup>®</sup> website.

### Lead-Free Designs (RoHS)

All Qseven<sup>®</sup>designs shall be created from lead-free components in order to be RoHS compliant.

### Qseven<sup>®</sup>Logo Usage

The Qseven<sup>®</sup> logo is freely available for members of SGeT e.V.. The logo can only be applied to products that are fully compliant to the specification of the Qseven<sup>®</sup> standard.

SGeT e.V. reserves the right to take legal action against any party that fails to comply with the rules stated above for Qseven<sup>®</sup> logo usage.

High resolution formats are available at the members area www.qseven-standard.org .

### Qseven<sup>®</sup> Name Usage

The Qseven<sup>®</sup> name is freely available for members of SGeT e.V.. The logo can only be applied to products that are fully compliant to the specification of the Qseven<sup>®</sup> standard.

SGeT e.V. reserves the right to take legal action against any party that fails to comply with the rules stated above for Qseven<sup>®</sup> name usage.

## Terminology

| Term               | Description                                                                                                                                                                                           |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARM/RISC           | The ARM is a 32-bit reduced instruction set computer (RISC) instruction set architecture (ISA) developed by ARM Holdings.                                                                             |

| X86                | The term x86 refers to a family of instruction set architectures based on the Intel 8086.                                                                                                             |

| PCI Express (PCIe) | Peripheral Component Interface Express. Next-generation high speed serialized I/O bus                                                                                                                 |

| PCI Express Lane   | One PCI Express Lane is a set of 4 signals that contains two differential lines for<br>Transmitter and two differential lines for Receiver. Clocking information is embedded into<br>the data stream. |

| x1, x2, x4         | x1 refers to one PCI Express Lane of basic bandwidth; x2 to a collection of two PCI Express Lanes; etc Also referred to as x1, x2, x4 link.                                                           |

| DDC                | Display Data Channel is an I <sup>2</sup> C bus interface between a display and a graphics adapter.                                                                                                   |

| DVI                | Digital Visual Interface is a video interface standard developed by the Digital Display Working Group (DDWG).                                                                                         |

| GBE                | Gigabit Ethernet                                                                                                                                                                                      |

| USB                | Universal Serial Bus                                                                                                                                                                                  |

| SATA               | Serial AT Attachment: serial interface standard for hard disks.                                                                                                                                       |

| HDA                | High Definition Audio                                                                                                                                                                                 |

| 12S                | Integrated Interchip Sound (I2S) is an electrical serial bus interface standard used for connecting digital audio devices together.                                                                   |

| HDMI               | High Definition Multimedia Interface. HDMI supports standard, enhanced, or high-definition video, plus multi-channel digital audio on a single cable.                                                 |

| TMDS               | Transition Minimized Differential Signaling. TMDS is a signaling interface defined by Silicon Image that is used for DVI and HDMI.                                                                    |

| DP<br>eDP          | (embedded) DisplayPort (DP/eDP) is a digital display interface developed by the Video Electronics Standards Association (VESA).                                                                       |

| LPC                | Low Pin-Count Interface: a low speed interface used for peripheral circuits such as Super I/O controllers, which typically combine legacy-device support into a single IC.                            |

| CAN                | Controller Area Network                                                                                                                                                                               |

| SPI                | Serial Peripheral Interface                                                                                                                                                                           |

| SDIO               | Secure Digital Input Output                                                                                                                                                                           |

| SMB                | System Management Bus                                                                                                                                                                                 |

| LVDS               | Low-Voltage Differential Signaling                                                                                                                                                                    |

| ACPI               | Advanced Control Programmable Interface                                                                                                                                                               |

| RoHS               | Restriction on Hazardous Substances: The Directive on the Restriction of the Use of Certain Hazardous Substances in Electrical and Electronic Equipment 2002/95/EC.                                   |

| N.C.               | Not connected                                                                                                                                                                                         |

| N.A.               | Not available                                                                                                                                                                                         |

| T.B.D.             | To be determined                                                                                                                                                                                      |

# Contents

| 1      | Qseven® Mechanical Characteristics           | .13 |

|--------|----------------------------------------------|-----|

| 1.1    | Mechanical Dimensions                        | .15 |

| 1.1.1  | Qseven® Module Outline                       |     |

| 1.1.2  | µQseven Module Outline                       | .16 |

| 1.1.3  | Edge Connector Dimensions of the PCB         | .17 |

| 1.1.4  | Connector and Cooling Plate Keep-Out         |     |

| 1.1.5  | Single Edge Finger Dimensions                |     |

| 1.1.6  | Location for Optional I/O Connector          |     |

| 1.2    | MXM Connector                                | 21  |

| 1.2.1  | Environmental Characteristics                |     |

| 1.2.2  | Electrical Characteristics                   |     |

| 1.2.3  | MXM Connector Dimensions                     |     |

| 1.2.4  | MXM Connector Footprint                      |     |

| 2      | Qseven® Feature Overview                     | .25 |

| 3      | Connector Pin Assignments                    | .26 |

| 3.1    | Signal Descriptions                          | .29 |

| 3.1.1  | PCI Express Interface Signals                | .30 |

| 3.1.2  | UART Interface Signals                       |     |

| 3.1.3  | Gigabit Ethernet Signals                     | .31 |

| 3.1.4  | Serial ATA Interface Signals                 |     |

| 3.1.5  | USB Interface Signals.                       | .32 |

| 3.1.6  | SDIO Interface Signals                       | .33 |

| 3.1.7  | High Definition Audio Signals/AC'97          | .33 |

| 3.1.8  | LVDS Flat Panel Signals                      |     |

| 3.1.9  | DisplayPort Interface Signals                |     |

| 3.1.10 | HDMI Interface Signals                       |     |

| 3.1.11 | LPC Interface Signals                        |     |

| 3.1.12 | SPI Interface Signals                        |     |

| 3.1.13 | CAN Bus Interface Signals                    |     |

| 3.1.14 | Input Power Pins                             |     |

| 3.1.15 | Power Control Signals                        |     |

| 3.1.16 | Power Management Signals                     |     |

| 3.1.17 | Miscellaneous Signals                        |     |

| 3.1.18 | Manufacturing Signals                        |     |

| 3.1.19 | Thermal Management Signals                   |     |

| 3.1.20 | Fan Control Implementation                   | .43 |

| 3.2    | Input Power Requirements                     | .43 |

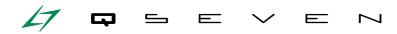

| 3.2.1  | Input Power Sequencing                       | .44 |

| 4      | Qseven® Signaling Budgets                    |     |

| 4.1    | PCI Express                                  | .45 |

| 4.1.1  | Qseven® Module PCI Express Budget Allocation | .45 |

| 4.1.2  | PCI Express Insertion Loss Budget            | .47 |

| 4.2    | Serial ATA                                   | .49 |

| 4.2.1  | Serial ATA Insertion Loss Budget             |     |

| 4.3    | USB 2.0                                      |     |

| 4.3.1  | USB 2.0 Insertion Loss Budget                |     |

| 4.4    | Gigabit Ethernet                             | .51 |

| 4.4.1  | Gigabit Ethernet Insertion Loss Budget       |     |

**Qseven Specification**

Page 9 of 55

V2.0 September 20, 2012

© 2013 SGeT e.V.

| 5     | Software Definitions                       | 53 |

|-------|--------------------------------------------|----|

| 5.1   | BIOS Implementations                       | 53 |

| 5.1.1 | LPC Super I/O Support                      |    |

| 5.2   | Embedded Application Programming Interface | 53 |

| 5.2.1 | General Information                        |    |

| 6     | Industry Specifications                    | 54 |

**Qseven Specification** Page 10 of 55 V2.0 September 20, 2012 © 2013 SGeT e.V.

## Tables

| Table 1-1 MXM Connector                                    |    |

|------------------------------------------------------------|----|

| Table 1-2 Environmental Characteristics for MXM Connectors | 21 |

| Table 1-3 Electrical Characteristics for MXM Connectors    | 22 |

| Table 2-1Qseven® Supported Features                        |    |

| Table 3-1 Connector Pinout Description                     |    |

| Table 3-2 Signal Terminology                               |    |

| Table 3-3 Signal Definition PCI Express                    |    |

| Table 3-4 Signal Definition of UART                        | 30 |

| Table 3-5 Signal Definition Ethernet                       |    |

| Table 3-6 Signal Definition SATA                           |    |

| Table 3-7 Signal Definition USB                            |    |

| Table 3-8 Signal Definition SDIO                           | 33 |

| Table 3-9 Signal Definition HDA/AC'97                      |    |

| Table 3-10 Signal LVDS                                     | 34 |

| Table 3-11 Signal Definition DisplayPort                   |    |

| Table 3-12 Signal Definition HDMI                          |    |

| Table 3-13 Signal Definition LPC                           |    |

| Table 3-14 Signal Definition SPI                           | 38 |

| Table 3-15 Signal Definition CAN Bus                       |    |

| Table 3-16 Signal Definition Input Power                   |    |

| Table 3-17 Signal Definition Power Control                 |    |

| Table 3-18 Signal Definition Power Management              | 40 |

| Table 3-19 Signal Definition Miscellaneous                 |    |

| Table 3-20 Signal Definition Manufacturing                 | 42 |

| Table 3-21 Signal Definition Thermal Management            | 43 |

| Table 3-22 Signal Definition Fan Control.                  |    |

| Table 3-23 Input Power Characteristics                     |    |

| Table 3-24: Input Power Sequencing                         |    |

| Table 4-1 PCI Express Budget Allocation                    |    |

| Table 4-2 Carrier Board PCI Express Insertion Loss Budget  |    |

| Table 4-3   SATA Gen 1 Loss Budget Allocation              |    |

| Table 4-4   SATA Gen2 Loss Budget Allocation.              |    |

| Table 4-5 USB 2.0 Loss Budget Allocation.                  |    |

| Table 4-6 Gigabit Ethernet Loss Budget Allocation          |    |

| Table 6-1 Industry Specifications                          | 54 |

## Figures

| Figure 1-1 Bottom Side Qseven® Module and Carrier Board Component Heights | 13 |

|---------------------------------------------------------------------------|----|

| Figure 1-2 Overall Height including Heatspreader of the Qseven® Module    | 14 |

| Figure 1-3 Mechanical Dimensions of the Qseven® Module                    | 15 |

| Figure 1-4: Mechanical Dimension of the µQseven Module                    | 16 |

| Figure 1-5 Edge Connector Dimensions of the Qseven® Module                | 17 |

| Figure 1-6 Qseven® Connector and Cooling Plate Keep-Out Area              | 18 |

| Figure 1-7: µQseven Keep-Out Area                                         |    |

| Figure 1-8 Edge Finger Dimensions of the Qseven® Module                   |    |

| Figure 1-9 Optional I/O Connector Area                                    |    |

| Figure 1-10 Carrier Board PCB Footprint for Foxconn MXM Connector         | 24 |

| Figure 1-11 Carrier Board PCB Footprint for Yamaichi MXM Connector        | 24 |

| Figure 3-1 Input Power Sequencing                                         | 44 |

| Figure 4-1 PCI Express Budget Allocation                                  | 45 |

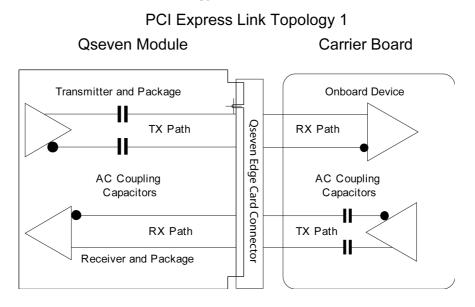

| Figure 4-2PCI Express Link Topology 1                                     |    |

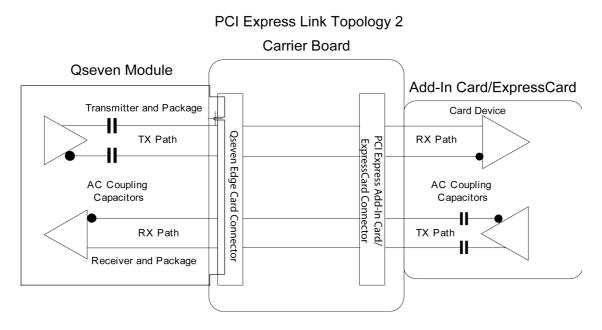

| Figure 4-3 PCI Express Link Topology 2                                    |    |

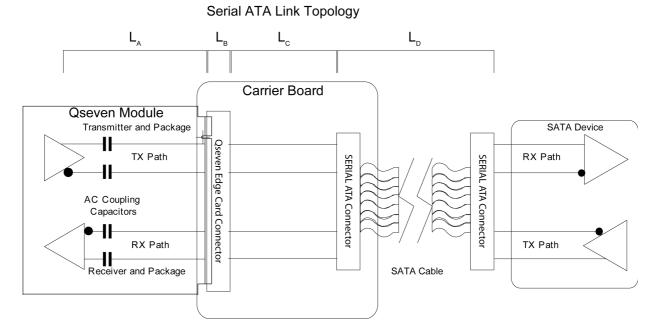

| Figure 4-4 Serial ATA Link Topology                                       |    |

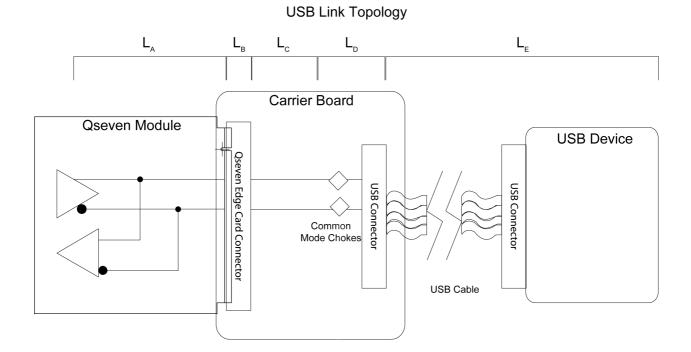

| Figure 4-5 USB 2.0 Link Topology                                          |    |

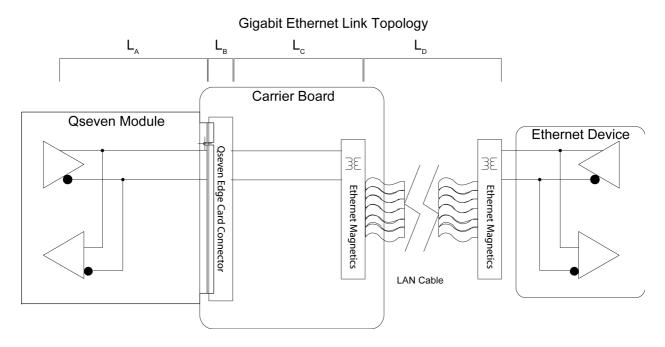

| Figure 4-6 Gigabit Ethernet Link Topology                                 | 51 |

# **1 Qseven<sup>®</sup> Mechanical Characteristics**

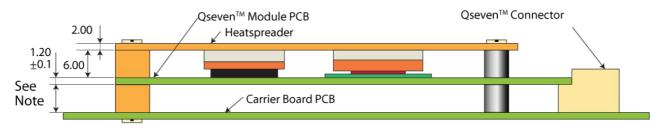

The Qseven<sup>®</sup> module, including the heatspreader plate, PCB thickness and bottom components, is up to approximately 12mm thick.

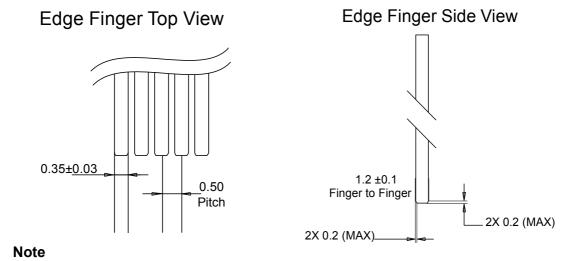

Edge-fingers on the module are referenced to the PCB slot center with an overall PCB thickness of  $1.2mm \pm 0.1$  measured across the fingers including the plating and/or metalization on both sides. Bevel is optional, but edge shall be free of burrs and shall not have sharp edges.

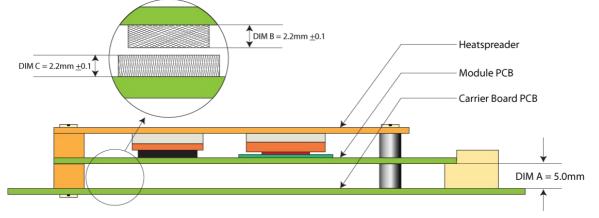

The components located on the top side of the module are up to 5.5mm high. Components mounted on the backside of the Qseven<sup>®</sup> module (in the space between the bottom surface of the module PCB and the top surface of the carrier board PCB) shall have a height of 2.2mm  $\pm 0.1$  (dimension 'B' in Figure 1-1). When using a MXM connector with a resulting height between carrier board and Qseven<sup>®</sup> module of 2.7mm, carrier board component placement below the Qseven<sup>®</sup> module is prohibited.

Carrier board component placement below the Qseven<sup>®</sup> module is only permitted when using a MXM connector with a resulting height between carrier board and Qseven<sup>®</sup> module of 5.0mm (dimension 'A' in Figure 1-1) and no carrier board component shall exceed a height of 2.2mm ±0.1 (dimension 'C' in Figure 1-1). Using carrier board topside components up to 2.2mm allows a gap of 0.3mm between carrier board topside components and the Qseven<sup>®</sup> module bottom side components. This may not be sufficient in some situations. In carrier board applications in which vibration or board flex is a concern, then the carrier board component height should be restricted to a value less than 2.2mm that yields a clearance that is sufficient for the application. Refer to Table 1-1 regarding MXM connector specifications.

Figure 1-1 Bottom Side Qseven<sup>®</sup> Module and Carrier Board Component Heights

The heatspreader offered for Qseven<sup>®</sup> modules acts as a thermal coupling device and is not a heat sink. Heat dissipation devices such as a heat sink with fan or heat pipe may need to be connected to the heatspreader. The dissipation of heat will fluctuate between different CPU boards. Refer to the Qseven<sup>®</sup> module's user's guide for heatspreader dimensions and specifications.

The standoffs for the heatspreader and carrier board must not exceed 5.6mm overall external diameter. This ensures that the standoff contact area does not exceed the defined mounting hole footprint on the Qseven<sup>®</sup> module. The screw that is to be used for mounting must be a metric thread M2.5 DIN7985 / ISO7045.

Qseven<sup>®</sup> modules are defined to feature ultra low power CPU and chipset solutions with an ultra low "Thermal Design Power" (TDP). Furthermore, the modules power consumption should not exceed 12W.

Note: Dimension is dependent on connector height used All measurements are in millimeters All dimensions without tolerance  $\pm 0.2$ mm

## **1.1 Mechanical Dimensions**

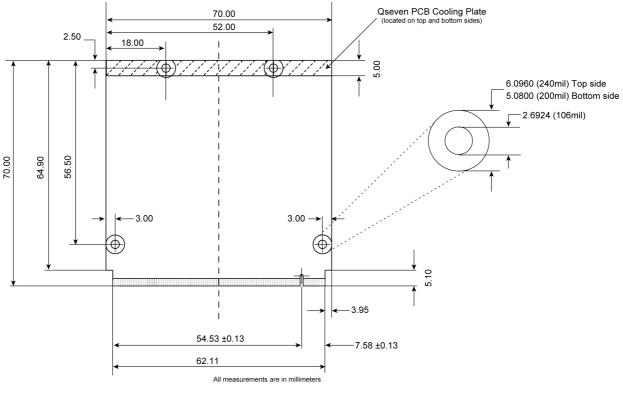

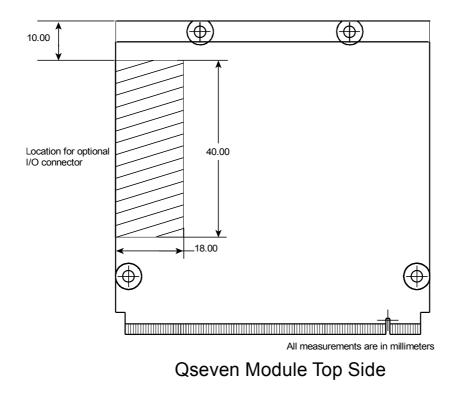

## 1.1.1 Qseven<sup>®</sup> Module Outline

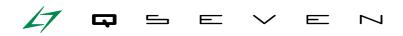

Figure 1-3 Mechanical Dimensions of the Qseven® Module

Qseven Module Top Side

The Qseven<sup>®</sup> PCB cooling plate shown in Figure 1-3 is to be used as a cooling interface between the Qseven<sup>®</sup> module and the application specific cooling solution.

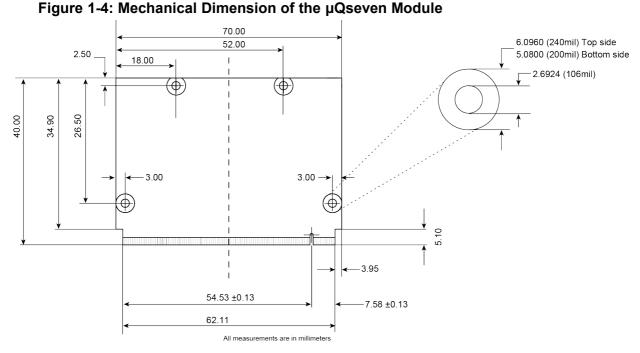

## 1.1.2 µQseven Module Outline

Qseven Module Top Side

#### Note Note

If one carrier board design is used for both  $\mu$ Qseven and Qseven<sup>®</sup>, the standoffs of the smaller  $\mu$ Qseven module will collide with the Qseven<sup>®</sup> module . To support both outlines, these standoffs of the  $\mu$ Qseven module should be removed when full sized Qseven<sup>®</sup> modules are used.

## 1.1.3 Edge Connector Dimensions of the PCB

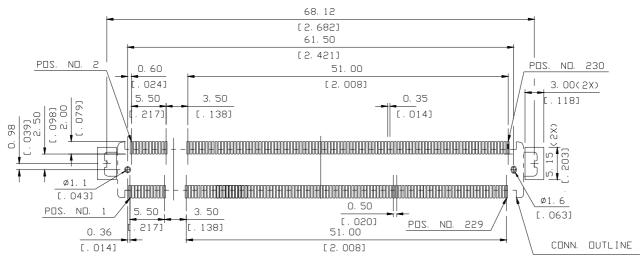

#### Figure 1-5 Edge Connector Dimensions of the Qseven® Module

#### Note

It is important to note that the edge fingers found on the top and bottom side are not mirrored and therefore have a slight offset from topside to bottom side.

**Qseven Specification**

Page 17 of 55

V2.0 September 20, 2012 © 2013 SGeT e.V.

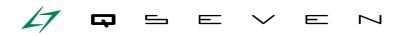

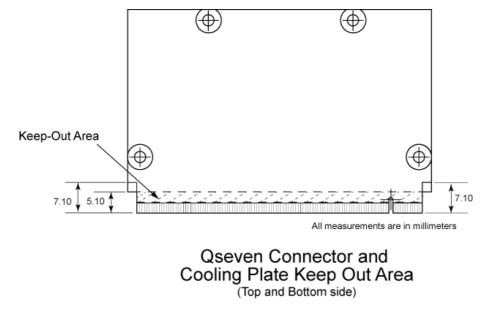

## 1.1.4 Connector and Cooling Plate Keep-Out

Figure 1-6 Qseven<sup>®</sup> Connector and Cooling Plate Keep-Out Area

It is not permitted to place components within the keep-out area defined above in order to avoid any mechanical collisions between components.

Figure 1-7: µQseven Keep-Out Area

## **1.1.5 Single Edge Finger Dimensions**

Figure 1-8 Edge Finger Dimensions of the Qseven<sup>®</sup> Module

Edge fingers are the same for both modules outlines.

## **1.1.6** Location for Optional I/O Connector

If an optional I/O connector, such as a Video Capture Port (VCP), is to be used it shall be placed in the I/O connector location area as defined in Figure 1-9.

This area is not a keep-out area and can be used for component placement if no additional I/O connector is required.

#### Figure 1-9 Optional I/O Connector Area

De Note

No location for an I/O connector is defined for µQseven Module.

## **1.2 MXM Connector**

The Qseven<sup>®</sup> module utilizes a 230-pin card-edge connector that is also used for PCI Express capable notebook graphics cards following the MXM specification. Therefore, this connector type is also known as a MXM connector.

The MXM edge connector is the result of an extensive collaborative design effort with the industry's leading notebook manufacturers. This collaboration has produced a robust, low-cost edge connector that is capable of handling high-speed serialized signals.

The MXM connector accommodates various connector heights for different carrier board applications needs. This specification suggests two connector heights, 7.8mm and 7.5mm.

| Table | 1-1 | MXM | Connector |

|-------|-----|-----|-----------|

|-------|-----|-----|-----------|

| Manufacturer | Part Number      | Specification    | Resulting height<br>between carrier board<br>and Qseven <sup>®</sup> module | Overall height of the MXM Connector |

|--------------|------------------|------------------|-----------------------------------------------------------------------------|-------------------------------------|

| Aces         | 88882-2Dxx       | 88882-2Dxx       | 5.0mm                                                                       | 7.5mm                               |

| Yamaichi     | BEC05230S9xFREDC | BEC05230S9xFREDC | 5.0 mm                                                                      | 7.8 mm                              |

| Foxconn      | AS0B32x-S78N-xH  | AS0B32x-S78N-xH  | 5.0 mm                                                                      | 7.8 mm                              |

#### Note Note

The connectors mentioned in Table 1-1 are only a partial list of what is offered by the manufacturers. For more information about additional variants contact the manufacturer.

## **1.2.1 Environmental Characteristics**

#### Table 1-2 Environmental Characteristics for MXM Connectors

| Parameter                    | Specification                                                                                                                                                                                                                                                                                    |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Durability                   | EIA-364-9<br>30 cycles                                                                                                                                                                                                                                                                           |

| Mating and<br>unmating force | EIA-364-13C<br>LIF/angled insertion styled cards:<br>Maximum insertion force: 1.3 kg<br>Maximum extraction force: 1.6 kg<br>Slide-in/side insertion styled cards<br>Maximum insertion force: 6.0 kg<br>Maximum extraction force: 4.6 kg<br>Note: numbers tabulated using a velocity of 25 mm/min |

| Vibration                    | EIA-364-28D – Test condition VII condition D<br>With a 40 x 40 mm block of 100 grams fastened and centered at the GPU center of a Type III PCB                                                                                                                                                   |

| Shock                        | EIA-364-27B – Test condition A<br>With a 40 x 40 mm block of 100 grams fastened and centered at the GPU center of a Type III PCB                                                                                                                                                                 |

## **1.2.2 Electrical Characteristics**

| Table 1-3 Electrical Characteristics for MXM Connectors |                                                                                                                                                                                                                                                    |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter                                               | Specification                                                                                                                                                                                                                                      |  |  |  |

| Low Level Contact<br>Resistance                         | EIA-364-23B – Specify which option used.<br>Do not use option 4.<br>Requirement: 40 m $\Omega$ maximum for initial measurements 50 m $\Omega$ maximum or Delta R = 20 m $\Omega$<br>maximum, whichever is less, for measurements after other tests |  |  |  |

| Insulation<br>Resistance                                | EIA-364-21C<br>Requirements: Initial testing 250 MΩ.<br>50 MΩ after other test procedures                                                                                                                                                          |  |  |  |

| Dielectric<br>Withstanding<br>Voltage                   | EIA-364-20B – Method B on one pair of upper adjacent contacts and on one pair of lower<br>adjacent contacts.<br>Connector is unmated and unmounted.<br>Barometric pressure at sea level.<br>Apply 0.25 kV AC, (50 Hz) for 1 minute.                |  |  |  |

| Current Rating                                          | Current requirement: Pins rated for 0.5 Amp continuous<br>The temperature rise above ambient shall not exceed 30 °C, where ambient condition is 25 °C<br>still air.                                                                                |  |  |  |

| Voltage Rating                                          | 50VDC per contact                                                                                                                                                                                                                                  |  |  |  |

| Impedance                                               | EIA-364-108<br>Impedance Requirements: 100 ± 20 $\Omega$ differential, 50 ± 10 $\Omega$ single ended.                                                                                                                                              |  |  |  |

| Insertion Loss                                          | EIA-364-101<br>Insertion Loss Requirements:<br>1 dB max up to 1.25 GHz;<br>$\leq$ [1.6* (F-1.25)+1] dB for 1.25 GHz < F $\leq$ 3.75 GHz (for example, $\leq$ 5 dB at F = 3.75 GHz)<br>where F is frequency in GHz.                                 |  |  |  |

| Return Loss                                             | EIA-364-108<br>Return Loss Requirements:<br>≤ -12 dB up to 1.3 GHz<br>≤ -7dB up to 2 GHz<br>≤ -4 dB up to 3.75 GHz                                                                                                                                 |  |  |  |

| Near End Crosstalk                                      | EIA-364-90 Crosstalk(NEXT) Requirements:<br>-32 dB max up to 1.25 GHz<br>$\leq$ -[32 – 2.4* (F – 1.25)] dB for 1.25 GHz < F $\leq$ 3.75 GHz (for example, $\leq$ -26 dB at F = 3.75 GHz)<br>where F is frequency in GHz.                           |  |  |  |

#### Table 1-3 Electrical Characteristics for MXM Connectors

## **1.2.3 MXM Connector Dimensions**

Refer to the used MXM connector's manufacturer's datasheet for information about the dimensions of the MXM connector.

## **1.2.4 MXM Connector Footprint**

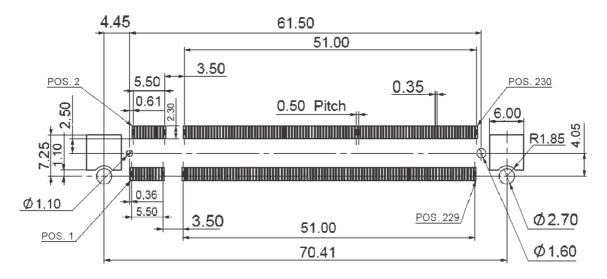

#### Figure 1-10 Carrier Board PCB Footprint for Foxconn MXM Connector

RECOMMENDED P.C.B. LAYOUT

Figure 1-11 Carrier Board PCB Footprint for Yamaichi MXM Connector

#### Note Note

The connectors mentioned in Table 1-1 are only a partial list of what is offered by the manufacturers. For more information about additional variants contact the manufacturer. Refer to the datasheet of the vendor for more details about the footprint. The footprints can slightly vary between different vendors.

**Qseven Specification**

Page 24 of 55

# 2 **Qseven<sup>®</sup> Feature Overview**

The Qseven<sup>®</sup> mandatory and optional features. Table 2-1 shows the minimum and maximum required configuration of the feature set.

| System I/O Interface                         | ARM/RISC Based<br>Minimum Configuration | X86 Based Minimum<br>Configuration | Maximum<br>Configuration |

|----------------------------------------------|-----------------------------------------|------------------------------------|--------------------------|

| PCI Express lanes                            | 0                                       | 1 (x1 link)                        | 4                        |

| Serial ATA channels                          | 0                                       | 0                                  | 2                        |

| USB 2.0 ports                                | 3                                       | 4                                  | 8                        |

| USB 3.0 ports                                | 0                                       | 0                                  | 2                        |

| LVDS channels<br>embedded DisplayPort        | 0<br>0                                  | 0<br>0                             | Dual Channel 24bits<br>2 |

| DisplayPort,<br>TMDS                         | 0                                       | 0                                  | 1                        |

| High Definition Audio / AC'97 /<br>I2S       | 0                                       | 0                                  | 1                        |

| Ethernet 10/100 Mbit/Gigabit                 | 0                                       | 0                                  | 1 (Gigabit Ethernet)     |

| UART                                         | 0                                       | 0                                  | 1                        |

| Low Pin Count bus                            | 0                                       | 0                                  | 1                        |

| Secure Digital I/O 8-bit<br>for SD/MMC cards | 0                                       | 0                                  | 1                        |

| System Management Bus                        | 0                                       | 1                                  | 1                        |

| I <sup>2</sup> C Bus                         | 1                                       | 1                                  | 1                        |

| SPI Bus                                      | 0                                       | 0                                  | 1                        |

| CAN Bus                                      | 0                                       | 0                                  | 1                        |

| Watchdog Trigger                             | 1                                       | 1                                  | 1                        |

| Power Button                                 | 1                                       | 1                                  | 1                        |

| Power Good                                   | 1                                       | 1                                  | 1                        |

| Reset Button                                 | 1                                       | 1                                  | 1                        |

| LID Button                                   | 0                                       | 0                                  | 1                        |

| Sleep Button                                 | 0                                       | 0                                  | 1                        |

| Suspend To RAM (S3 mode)                     | 0                                       | 0                                  | 1                        |

| Wake                                         | 0                                       | 0                                  | 1                        |

| Battery low alarm                            | 0                                       | 0                                  | 1                        |

| Thermal control                              | 0                                       | 0                                  | 1                        |

| FAN control                                  | 0                                       | 0                                  | 1                        |

#### Table 2-1Qseven<sup>®</sup> Supported Features

# **3** Connector Pin Assignments

There are 115 edge fingers on the top and bottom side of the Qseven<sup>®</sup> module that mate with the MXM connector. Table 3-1 lists the pin assignments for all 230 edge fingers.

| Pin | Signal                    | Pin | Signal                |

|-----|---------------------------|-----|-----------------------|

| 1   | GND                       | 2   | GND                   |

| 3   | GBE_MDI3-                 | 4   | GBE_MDI2-             |

| 5   | GBE_MDI3+                 | 6   | GBE_MDI2+             |

| 7   | GBE_LINK100#              | 8   | GBE_LINK1000#         |

| 9   | GBE_MDI1-                 | 10  | GBE_MDI0-             |

| 11  | GBE_MDI1+                 | 12  | GBE_MDI0+             |

| 13  | GBE_LINK#                 | 14  | GBE_ACT#              |

| 15  | GBE_CTREF                 | 16  | SUS_S5#               |

| 17  | WAKE#                     | 18  | SUS_S3#               |

| 19  | SUS_STAT#                 | 20  | PWRBTN#               |

| 21  | SLP_BTN#                  | 22  | LID_BTN#              |

| 23  | GND                       | 24  | GND                   |

|     | KEY                       |     | KEY                   |

| 25  | GND                       | 26  | PWGIN                 |

| 27  | BATLOW#                   | 28  | RSTBTN#               |

| 29  | SATA0_TX+                 | 30  | SATA1_TX+             |

| 31  | SATA0_TX-                 | 32  | SATA1_TX-             |

| 33  | SATA_ACT#                 | 34  | GND                   |

| 35  | SATA0_RX+                 | 36  | SATA1_RX+             |

| 37  | SATA0_RX-                 | 38  | SATA1_RX-             |

| 39  | GND                       | 40  | GND                   |

| 41  | BIOS_DISABLE# / BOOT_ALT# | 42  | SDIO_CLK#             |

| 43  | SDIO_CD#                  | 44  | SDIO_LED              |

| 45  | SDIO_CMD                  | 46  | SDIO_WP               |

| 47  | SDIO_PWR#                 | 48  | SDIO_DAT1             |

| 49  | SDIO_DAT0                 | 50  | SDIO_DAT3             |

| 51  | SDIO_DAT2                 | 52  | SDIO_DAT5             |

| 53  | SDIO_DAT4                 | 54  | SDIO_DAT7             |

| 55  | SDIO_DAT6                 | 56  | RSVD                  |

| 57  | GND                       | 58  | GND                   |

| 59  | HDA_SYNC / I2S_WS         | 60  | SMB_CLK / GP1_I2C_CLK |

| 61  | HDA_RST# / I2S_RST#       | 62  | SMB_DAT / GP1_I2C_DAT |

| 63  | HDA_BITCLK / I2S_CLK      | 64  | SMB_ALERT#            |

| 65  | HDA_SDI / I2S_SDI         | 66  | GP0_I2C_CLK           |

| 67  | HDA_SDO / I2S_SDO         | 68  | GP0_I2C_DAT           |

#### Table 3-1 Connector Pinout Description

**Qseven Specification**

V2.0 September 20, 2012 © 2013 SGeT e.V.

| Pin | Signal                        | Pin | Signal                      |

|-----|-------------------------------|-----|-----------------------------|

| 69  | THRM#                         | 70  | WDTRIG#                     |

| 71  | THRMTRIP#                     | 72  | WDOUT                       |

| 73  | GND                           | 74  | GND                         |

| 75  | USB_P7- / USB_SSTX0-          | 76  | USB_P6- / USB_SSRX0-        |

| 77  | USB P7+/USB SSTX0+            | 78  | USB P6+ / USB SSRX0+        |

| 79  | USB_6_7_OC#                   | 80  | USB_4_5_OC#                 |

| 81  | USB P5-/USB SSTX1-            | 82  | USB P4-/USB SSRX1-          |

| 83  | USB P5+/USB SSTX1+            | 84  | USB P4+/USB SSRX1+          |

| 85  | USB_2_3_OC#                   | 86  | USB 0 1 OC#                 |

| 87  | USB_P3-                       | 88  | USB_P2-                     |

| 89  | <br>USB_P3+                   | 90  | <br>USB_P2+                 |

| 91  | USB_CC                        | 92  | USB ID                      |

| 93  | USB_P1-                       | 94  | USB P0-                     |

| 95  | USB P1+                       | 96  | <br>USB_P0+                 |

| 97  | GND                           | 98  | GND                         |

| 99  | eDP0 TX0+/ LVDS A0+           | 100 | eDP1 TX0+/LVDS B0+          |

| 101 | eDP0 TX0-/LVDS A0-            | 102 | eDP1 TX0-/LVDS B0-          |

| 103 | eDP0_TX1+ / LVDS_A1+          | 104 | <br>eDP1_TX1+ / LVDS_B1+    |

| 105 | eDP0_TX1- / LVDS_A1-          | 106 | eDP1_TX1- / LVDS_B1-        |

| 107 | eDP0_TX2+ / LVDS_A2+          | 108 | eDP1_TX2+ / LVDS_B2+        |

| 109 | eDP0_TX2- / LVDS_A2-          | 110 | eDP1_TX2- / LVDS_B2-        |

| 111 | LVDS_PPEN                     | 112 | LVDS_BLEN                   |

| 113 | eDP0_TX3+ / LVDS_A3+          | 114 | eDP1_TX3+ / LVDS_B3+        |

| 115 | eDP0_TX3- / LVDS_A3-          | 116 | eDP1_TX3- / LVDS_B3-        |

| 117 | GND                           | 118 | GND                         |

| 119 | eDP0_AUX+ / LVDS_A_CLK+       | 120 | eDP1_AUX+ / LVDS_B_CLK+     |

| 121 | eDP0_AUX- / LVDS_A_CLK-       | 122 | eDP1_AUX- / LVDS_B_CLK-     |

| 123 | LVDS_BLT_CTRL<br>/GP_PWM_OUT0 | 124 | GP_1-Wire_Bus               |

| 125 | GP2_I2C_DAT /<br>LVDS_DID_DAT | 126 | eDP0_HPD# /<br>LVDS_BLC_DAT |

| 127 | GP2_I2C_CLK /<br>LVDS_DID_CLK | 128 | eDP1_HPD# /<br>LVDS_BLC_CLK |

| 129 | CAN0_TX                       | 130 | CAN0_RX                     |

| 131 | DP_LANE3+ / TMDS_CLK+         | 132 | RSVD (Differential Pair)    |

| 133 | DP_LANE3- / TMDS_CLK-         | 134 | RSVD (Differential Pair)    |

| 135 | GND                           | 136 | GND                         |

| 137 | DP_LANE1+ / TMDS_LANE1+       | 138 | DP_AUX+                     |

| 139 | DP_LANE1- / TMDS_LANE1-       | 140 | DP_AUX-                     |

| 141 | GND                           | 142 | GND                         |

| 143 | DP_LANE2+ / TMDS_LANE0+       | 144 | RSVD (Differential Pair)    |

| 145 | DP_LANE2- / TMDS_LANE0-       | 146 | RSVD (Differential Pair)    |

| 147 | GND                           | 148 | GND                         |

**Qseven Specification**

Page 27 of 55

V2.0 September 20, 2012

© 2013 SGeT e.V.

| 149       DP_LANEO+ / TMDS_LANE2+       150       HDMI_CTRL_DAT         151       DP_LANEO- / TMDS_LANE2-       152       HDMI_CTRL_CLK         153       DP_HDMI_HPD#       154       RSVD         155       PCIE_CLK_REF+       156       PCIE_RST#         159       GND       160       GND         161       PCIE3_TX+       162       PCIE3_RX+         163       PCIE3_TX-       164       PCIE3_RX-         164       PCIE3_RX-       166       GND         167       PCIE2_TX+       168       PCIE2_RX-         169       PCIE1_TX+       174       PCIE1_RX-         170       PCIE1_TX+       174       PCIE1_RX+         173       PCIE1_TX-       176       PCIE1_RX-         174       UART0_RX       178       UART0_CTS#         175       PCIE0_TX+       180       PCIE0_RX-         181       PCIE0_TX-       182       PCIE0_RX-         183       GND       184       GND         184       GND       186       LPC_AD1 / GPIO3         185       LPC_CLK / GPIO4       190       LPC_LDRO# / GPIO5         191       SERIRQ / GPIO6       192 <td< th=""><th><b>D</b>:</th><th></th><th><b>D</b>'</th><th></th></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>D</b> : |                 | <b>D</b> ' |                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|------------|--------------------|

| 151         DP_LANEO- / TMDS_LANE2-         152         HDMI_CTRL_CLK           153         DP_HDMI_HPD#         154         RSVD           155         PCIE_CLK_REF+         156         PCIE_WAKE#           157         PCIE_CLK_REF-         158         PCIE_RST#           159         GND         160         GND           161         PCIE3_TX+         162         PCIE3_RX-           163         PCIE2_TX+         164         PCIE2_RX-           164         PCIE2_RX+         168         PCIE2_RX-           176         PCIE1_TX+         170         PCIE2_RX-           177         UART0_TX         172         UART0_RTS#           178         PCIE1_TX+         174         PCIE1_RX-           179         PCIE0_TX+         178         UART0_CTS#           179         PCIE0_TX+         180         PCIE0_RX-           183         GND         184         GND           184         LPC_ADD / GPIO2         188         LPC_AD1 / GPIO3           185         LPC_AD2 / GPIO2         188         LPC_AD3 / GPIO3           189         LPC_CLK / GPIO4         190         LPC_FRAME# / GPIO5           191         SERIRQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pin        | Signal          | Pin        | Signal             |

| 153       DP_HDMI_HPD#       154       RSVD         155       PCIE_CLK_REF+       156       PCIE_WAKE#         157       PCIE_CLK_REF-       158       PCIE_RST#         159       GND       160       GND         161       PCIE3_TX+       162       PCIE3_RX+         163       PCIE3_TX-       164       PCIE3_RX-         165       GND       166       GND         167       PCIE2_TX+       168       PCIE2_RX-         170       PCIE2_TX-       170       PCIE2_RX-         171       UARTO_TX       172       UARTO_RTS#         173       PCIE1_TX+       174       PCIE1_RX-         174       PATO_RX       178       UARTO_CTS#         175       PCIE0_TX+       180       PCIE0_RX-         178       PATO_RX       178       UARTO_CTS#         179       PCIE0_TX-       182       PCIE0_RX-         181       PCIE0_TX-       182       PCIE0_RX-         183       GND       184       GND         185       LPC_AD2 / GPIO2       188       LPC_AD3 / GPIO3         189       LPC_CLK / GPIO4       190       LPC_FRAME# / GPIO5      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -          |                 |            |                    |

| Image: https://www.setup.op/1000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |                 |            | HDMI_CTRL_CLK      |

| Image: Constraint of the second state of th | 153        | DP_HDMI_HPD#    | 154        | RSVD               |

| Image: Section of the sectio | 155        | PCIE_CLK_REF+   | 156        | PCIE_WAKE#         |

| Initial         PCIE3_TX+         Initial         PCIE3_RX+           163         PCIE3_TX-         164         PCIE3_RX-           165         GND         166         GND           167         PCIE2_TX+         168         PCIE2_RX+           169         PCIE2_TX-         170         PCIE2_RX-           171         UART0_TX         172         UART0_RTS#           173         PCIE1_TX+         174         PCIE1_RX+           175         PCIE1_TX-         176         PCIE0_RX+           177         UART0_RX         178         UART0_CTS#           179         PCIE0_TX+         180         PCIE0_RX+           181         PCIE0_TX-         182         PCIE0_RX-           183         GND         184         GND           185         LPC_AD2 / GPIO2         188         LPC_AD3 / GPIO3           189         LPC_CLK / GPIO4         190         LPC_LDRQ# / GPIO7           193         VCC_RTC         194         SPKR / GP_PWM_OUT2           195         FAN_TACHOIN /<br>GP_TIMER_IN         196         FAN_PWMOUT /<br>GP_FWM_OUT1           197         GND         198         GND           198         SPL_MOSI <td>157</td> <td>PCIE_CLK_REF-</td> <td>158</td> <td>PCIE_RST#</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 157        | PCIE_CLK_REF-   | 158        | PCIE_RST#          |

| International         International           163         PCIE3_TX-         164         PCIE3_RX-           165         GND         166         GND           167         PCIE2_TX+         168         PCIE2_RX+           169         PCIE2_TX-         170         PCIE2_RX-           171         UARTO_TX         172         UARTO_RTS#           173         PCIE1_TX+         174         PCIE1_RX+           175         PCIE1_TX-         176         PCIE1_RX-           177         UARTO_RX         178         UARTO_CTS#           179         PCIE0_TX+         180         PCIE0_RX-           181         PCIE0_TX-         182         PCIE0_RX-           183         GND         184         GND           185         LPC_AD0 / GPIO0         186         LPC_AD3 / GPIO3           188         LPC_CLK / GPIO4         190         LPC_FRAME# / GPIO5           191         SERRQ / GPIO6         192         LPC_LDRQ# / GPIO7           193         VCC_RTC         194         SPKR / GP_PVM_OUT2           195         FAN_TACHOIN /<br>GP_TIMER_IN         196         FAN_PWMOUT /<br>GP_FWM_OUT1           197         GND         198 <td>159</td> <td>GND</td> <td>160</td> <td>GND</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 159        | GND             | 160        | GND                |

| 165         GND         166         GND           167         PCIE2_TX+         168         PCIE2_RX+           169         PCIE2_TX-         170         PCIE2_RX-           171         UART0_TX         172         UART0_RTS#           173         PCIE1_TX+         174         PCIE1_RX+           175         PCIE1_TX-         176         PCIE1_RX-           177         UART0_RX         178         UART0_CTS#           179         PCIE0_TX+         180         PCIE0_RX-           181         PCIE0_TX-         182         PCIE0_RX-           183         GND         184         GND           185         LPC_AD0 / GPIO0         186         LPC_AD1 / GPIO1           187         LPC_CLK / GPIO4         190         LPC_FRAME# / GPIO5           191         SERRQ / GPIO6         192         LPC_LDRQ# / GPIO7           193         VCC_RTC         194         SPKR / GP_PWM_OUT2           195         FAN_TACHOIN /<br>GP_TIMER_IN         196         FAN_PWMOUT /<br>GP_PWM_OUT1           197         GND         198         GND           198         SPL_SCK         204         MFG_NC4           205         VCC_SSB <td>161</td> <td>PCIE3_TX+</td> <td>162</td> <td>PCIE3_RX+</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 161        | PCIE3_TX+       | 162        | PCIE3_RX+          |

| 167         PCIE2_TX+         168         PCIE2_RX+           169         PCIE2_TX-         170         PCIE2_RX-           171         UART0_TX         172         UART0_RTS#           173         PCIE1_TX+         174         PCIE1_RX-           175         PCIE1_TX-         176         PCIE1_RX-           177         UART0_RX         178         UART0_CTS#           179         PCIE0_TX+         180         PCIE0_RX-           181         PCIE0_TX-         182         PCIE0_RX-           183         GND         184         GND           185         LPC_ADD / GPIO0         186         LPC_ADJ / GPIO3           189         LPC_CLK / GPIO4         190         LPC_FRAME# / GPIO5           191         SERIRQ / GPIO6         192         LPC_LDRQ# / GPIO7           193         VCC_RTC         194         SPKR / GP_PWM_OUT2           195         FAN_TACHOIN /<br>GP_TIMER_IN         196         FAN_PWMOUT /<br>GP_PWM_OUT1           197         GND         198         GND           199         SPI_MOSI         200         SPI_CS0#           201         SPI_SCK         204         MFG_NC4           205 <td< td=""><td>163</td><td>PCIE3_TX-</td><td>164</td><td>PCIE3_RX-</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 163        | PCIE3_TX-       | 164        | PCIE3_RX-          |